# UM32x42x 定时器应用指南

版本: V1.0

广芯微电子(广州)股份有限公司

http://www.unicmicro.com/

AN2402 条款协议

### 条款协议

本文档的所有部分,其著作产权归广芯微电子(广州)股份有限公司(以下简称广芯微电子) 所有,未经广芯微电子授权许可,任何个人及组织不得复制、转载、仿制本文档的全部或部分组件。 本文档没有任何形式的担保、立场表达或其他暗示,若有任何因本文档或其中提及的产品所有资讯 所引起的直接或间接损失,广芯微电子及所属员工恕不为其担保任何责任。除此以外,本文档所提 到的产品规格及资讯仅供参考,内容亦会随时更新,恕不另行通知。

- 本文档中所记载的关于电路、软件和其他相关信息仅用于说明半导体产品的操作和应用实例。

用户如在设备设计中应用本文档中的电路、软件和相关信息,请自行负责。对于用户或第三方因使用上述电路、软件或信息而遭受的任何损失,广芯微电子不承担任何责任。

- 2. 在准备本文档所记载的信息的过程中,广芯微电子已尽量做到合理注意,但是,广芯微电子并不保证这些信息都是准确无误的。用户因本文档中所记载的信息的错误或遗漏而遭受的任何损失,广芯微电子不承担任何责任。

- 3. 对于因使用本文档中的广芯微电子产品或技术信息而造成的侵权行为或因此而侵犯第三方的专利、版权或其他知识产权的行为,广芯微电子不承担任何责任。本文档所记载的内容不应视为对广芯微电子或其他人所有的专利、版权或其他知识产权作出任何明示、默示或其它方式的许可及授权。

- 4. 使用本文档中记载的广芯微电子产品时,应在广芯微电子指定的范围内,特别是在最大额定值、电源工作电压范围、热辐射特性、安装条件以及其他产品特性的范围内使用。对于在上述指定范围之外使用广芯微电子产品而产生的故障或损失,广芯微电子不承担任何责任。

- 5. 虽然广芯微电子一直致力于提高广芯微电子产品的质量和可靠性,但是,半导体产品有其自身的具体特性,如一定的故障发生率以及在某些使用条件下会发生故障等。此外,广芯微电子产品均未进行防辐射设计。所以请采取安全保护措施,以避免当广芯微电子产品在发生故障而造成火灾时导致人身事故、伤害或损害的事故。例如进行软硬件安全设计(包括但不限于冗余设计、防火控制以及故障预防等)、适当的老化处理或其他适当的措施等。

## 目录

| 1 | 摘要                                           |            |

|---|----------------------------------------------|------------|

| 2 | PLL 倍频应用                                     |            |

| 3 | 高级定时器 TIM0/7 的硬件移相3.1 在中央对齐计数模式下使用非对称 PWM 模式 | 3          |

| 4 | GPIO 与 TIM 配合应用                              | <br>3<br>8 |

| 5 | TIM 使用注意要点                                   |            |

| 6 | 版木维护                                         | 10         |

AN2402 摘要

## 1 摘要

本篇应用笔记主要介绍UM32x42x芯片定时器模块(TIM)的一些应用细节。TIM的基本使用 方法可参考UM32x42x芯片用户手册,本应用笔记旨在对用户手册未提及但又相对常见的应用进行 补充,并提出了一些使用时应注意的点,以帮助用户更好更快地使用UM32x42x芯片的TIM模块。

本篇应用笔记主要包括:

- PLL倍频应用

- 高级定时器0/7的硬件移相

- GPIO与TIM的配合应用

- TIM使用注意要点

注: 具体功能及寄存器的操作等相关事项请以用户手册为准。

AN2402 PLL 倍频应用

# 2 PLL 倍频应用

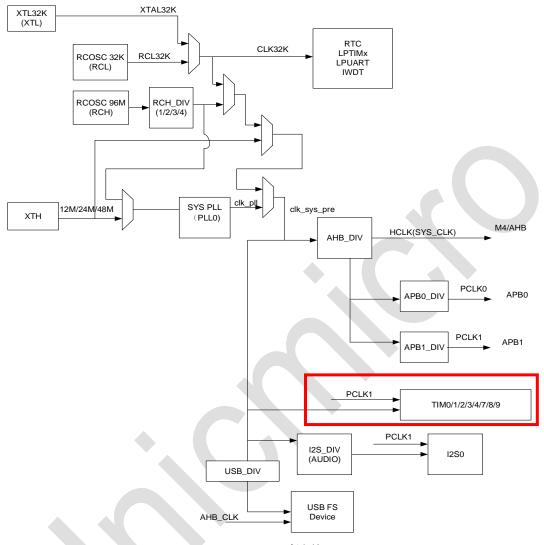

图 2-1: 时钟单元

由图 2-1 可以看到 TIMO/1/2/3/4/8/9 的时钟源可以选择 PCLK1 或 PLL 倍频输出。默认时钟源为 PCLK1,可通过 RCM 模块的 CFGR1 寄存器第 20 位 TIM\_CLK\_SEL1 进行选择配置。 TIM\_CLK\_SEL1 为 0 时,TIM 时钟源为 PCLK1; TIM\_CLK\_SEL1 为 1 时,TIM 时钟源为 PLL 倍频输出。目前测试 PLL 倍频至 336MHz 时 TIM 仍可稳定使用。

## 3 高级定时器 TIM0/7 的硬件移相

高级定时器TIMO/7可以通过以下两种不同的方式实现硬件移相功能:

- 中央对齐计数模式下使用非对称PWM模式

- 在边沿对齐计数模式下使用组合PWM模式

### 3.1 在中央对齐计数模式下使用非对称 PWM 模式

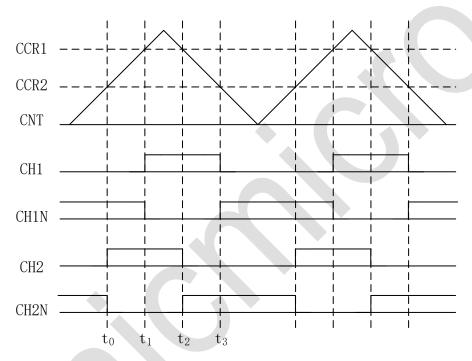

图 3-1: 中央对齐计数模式下使用非对称 PWM 模式实现硬件移相示意图

非对称 PWM 模式在 TIM 向上计数时以自身通道比较值作为翻转基准,在 TIM 向下计数时以相邻通道比较值作为翻转基准。以 TIM0 的 CH1 和 CH2 为例,在 CNT 向上计数时,CH1 以自身比较值(CCR1)为基准,CH2 以 CCR2 为基准,分别在  $t_1$  和  $t_0$  发生翻转;而在 CNT 向下计数时,CH1 以 CCR2 为基准,CH2 以 CCR1 为基准,分别发生翻转。这样会使 CH1 和 CH2 错开  $t_1$ - $t_0$  的相差,实现硬件移相。类似的,CH3 和 CH4 也可以实现这样的操作,输出一组移相的 PWM,但要注意CH4 是没有互补通道的。一个高级定时器最多可以使用这种方式输出三对互补 PWM 移相 PWM。

需要注意的是,由于使用了中央对齐模式,且只有在改变计数方向时才会互换比较基准,因此这种方式实现的移相波形必然会有交叠,最极限的情况便是 CCR1 为计数周期值,CCR2 为 0,输出的波形会在中央紧贴,如图 3-1 所示。而由于两通道的输出波形必然存在交叠,故这种移相方式的移相范围也与输出的占空比有关,当输出占空比较小时移相范围也会变小。

这种移相方式可用于电机控制等使用中央对齐模式的场合。

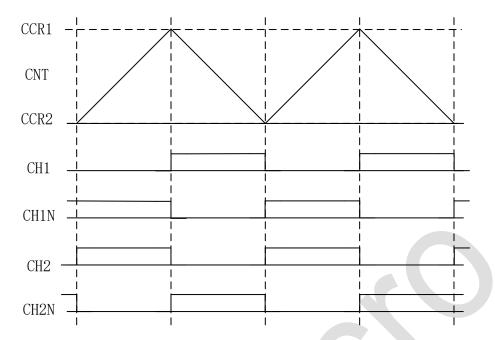

图 3-2: 中央对齐计数模式下使用非对称 PWM 模式实现硬件移相的极限情况

### 3.2 在边沿对齐计数模式下使用组合 PWM 模式

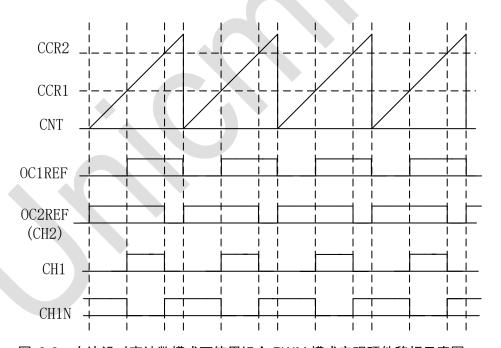

图 3-3: 在边沿对齐计数模式下使用组合 PWM 模式实现硬件移相示意图

组合 PWM 模式可将相邻两通道的状态进行逻辑运算。以 TIM0 的 CH1、CH2 为例,CH1 设置为组合 PWM 模式 2,该模式下 CH1 的状态(OC1REF)会按 PWM 模式 2 生成。当 CNT>CCR1时,OC1REF 为高,同时 CH1 的输出为 OC1REF和 OC2REF的逻辑与。CH2 设置为 PWM 模式 1,当 CNT>CCR2时,OC2REF为低。如图 3-3 所示,可以通过设置 CCR1 的值决定 CH1 何时置高,设置 CCR2 决定 CH1 何时拉低,即 CCR1 决定相位,CCR2-CCR1 决定脉宽。同理,CH3 和 CH4 也可使用相同的配置实现可自由决定相位和脉宽的 PWM 输出。一个高级定时器最多可通过这

种方式输出两对互补 PWM 移相输出。

相比在中央对齐模式下使用非对称 PWM 实现硬件移相,这种方法更加灵活自由,且边沿对齐模式天然比中央对齐模式的频率高一倍,应用范围更加广泛。但由于该方法牺牲了一路 PWM 通道用来决定输出的脉宽,故该方法的输出通道数较另一种方法更少。

这种移相方式可用于边沿对齐模式的应用场合。

## 4 GPIO 与 TIM 配合应用

当使用TIM作输出或捕获时往往需要通过GPIO作为媒介。而TIM与GPIO是相对独立的两个模块,他们的一些功能是可以叠加使用的。

### 4.1 高频 PWM 场合使用更大的电流驱动 GPIO 以缩窄死区

在输出高频互补PWM时,死区时间往往会变得更窄,这要求IO具有更大的驱动能力,以便更快地翻转电平,否则可能会使两个通道的波形重叠。这个问题在开启了PLL倍频后更为明显,因为TIM的时钟更快,死区精度更高。

7.4.19 → 驱动能力寄存器 (GPIO\_DS)

偏移地址: 0x4C√ 复位值: 0x5555·5555√

| ∲     | 名称₽ | 属性₽  | 复位值₽         | 描述。                                                                                           | ¢) |

|-------|-----|------|--------------|-----------------------------------------------------------------------------------------------|----|

| 31:0₽ | DS₽ | R/W₽ | 0x5555_5555₽ | 32 位寄存器,每 2 位对应 1 个 IO;选择<br>GPIO 输出驱动能力: ゼ<br>00: 2mAゼ<br>01: 6mAゼ<br>10: 14mAゼ<br>11: 20mAゼ | C. |

图 4-1: GPIO 的 DS 寄存器

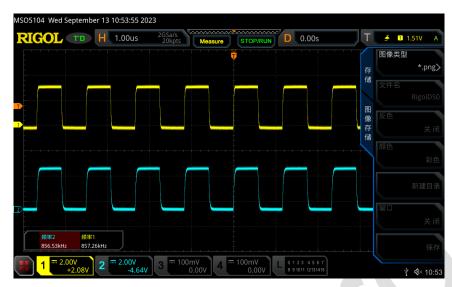

此时可配置GPIO模块的DS寄存器(见图4-1)来增大IO的驱动电流。图4-2为使用不同电流驱动的PWM波形,测试时开启PLL倍频将TIM的时钟源倍频到了480MHz,死区时间设置为1。可以看到驱动电流为2mA时,两路波形无可避免地发生了交叠,而驱动电流为6mA时情况则好了很多。需要注意的是,随着驱动电流增大,波形的振铃效应也愈发明显,在工程应用时应注意其带来的影响。

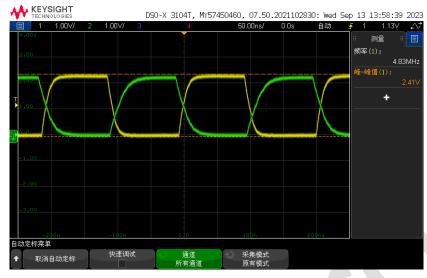

#### (a) 驱动电流为 2mA

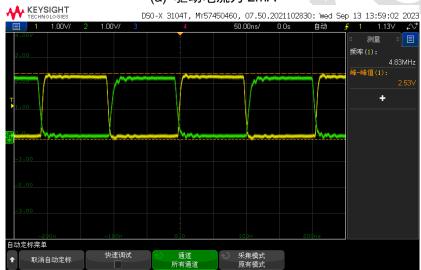

#### (b) 驱动电流为 6mA

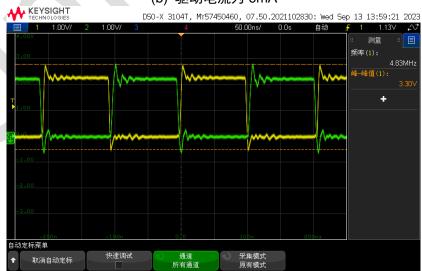

(c) 驱动电流为 14mA

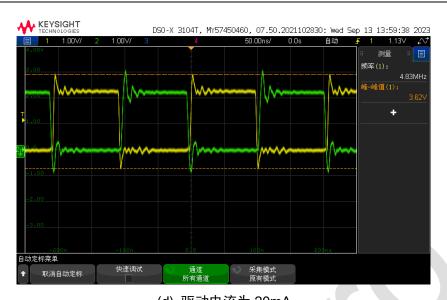

(d) 驱动电流为 20mA 图 4-2:使用不同电流驱动的 PWM 的波形

## 4.2 **GPIO** 状态检测

在使用 TIM 捕获 PWM 时,若捕获的 PWM 占空比为 0%或 100%,由于没有上下边沿的变化,TIM 将无法触发捕获。若要求必须获取到 0%或 100%占空比,则可使用更新中断或另一通道的比较中断,将计数周期或比较值设为捕获的波形频率,在中断里读取 GPIO 的 IDATA 寄存器。无需重配 GPIO,IDATA 寄存器会如实反应 GPIO 的状态。

### 4.3 多个 GPIO 同时复用为同一 PWM 通道

若需要多个同步的通道,可以直接将多个 GPIO 复用为同一 PWM 通道,他们会输出相同的 PWM 波形。如将 PA5 和 PA7 同时复用为 TIM7 的 CH1N 通道,可以得到的波形如图 4-3 所示,可以看到它们的输出是一样的。

图 4-3: PA5 (黄)与 PA7 (蓝)同时复用为 TIM7 CH1N 通道波形

## 4.4 施密特与捕获滤波

当外界环境较为恶劣时,往往会给 TIM 捕获开启滤波功能。同时也可(在不影响功能的条件下)将 GPIO 配置为施密特输入模式,进一步提升抗干扰能力。

AN2402 TIM 使用注意要点

## 5 TIM 使用注意要点

### 5.1 高级定时器刹车状态配置

相较于通用定时器,高级定时器 TIM0/7 可以在 SYSREG 的 TIMCFGR 寄存器的 TIM0\_BRKR和 TIM7\_BRKR 位额外设定刹车时的 PWM 通道状态,具体逻辑如下表所示:

| BRKR | OSSR | 刹车时输出                       |

|------|------|-----------------------------|

| 0    | 0    | OCxP                        |

| 1    | 0    | 0                           |

| 0    | 1    | OCxP                        |

| 1    | 1    | 设计不支持,请不要将 BRKR 和 OSSR 同时置一 |

表 5-1: 高级定时器刹车输出状态表

OSSR 为 0 时 TIM 不会再控制 IO,通用定时器没有 BRKR 位,此时输出为 0;高级定时器可通过 BRKR 位设置状态。需要注意的是,BRKR 和 OSSR 不可以同时为 1,请避免出现这种情况。

### 5.2 换相中断触发条件

TIM 的换相中断(COM 中断)的触发条件除了换相事件,还会被其他定时器的内部互联触发信号所触发。参考错误!未找到引用源。,以 TIMO 为例,也就是说在 TIM1、TIM2、TIM3、TIM4 的触发事件发生时,无论 TIM0 是否开启了从定时器内部触发功能,TIM0 的 COM 中断都会被触发。所以在使用多定时器的场合,若需使用 COM 中断要格外注意。

需要注意的是,不能将 COM 事件与 COM 中断混为一谈, COM 事件的触发条件可以通过 CR2 的 CCUS 位设置,并且可以更新预装载的捕获/比较控制位;而 COM 中断只是一个中断,并没有更新预装载的功能。

| TIMx Interconnect                  |                                  |           |           |           |           |           |           |           |

|------------------------------------|----------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Source<br>(TIMx Trigger<br>Output) | . Inputs<br>(TIMx Trigger Input) |           |           |           |           |           |           |           |

| TIM0_TRGO                          |                                  | TIM1_ITR0 | TIM2_ITR0 | TIM3_ITR0 |           | TIM7_ITR0 | -         | -         |

| TIM1_TRGO                          | TIM0_ITR1                        | -         | TIM2_ITR1 | TIM3_ITR1 | TIM4_ITR0 | TIM7_ITR1 | TIM8_ITR2 | TIM9_ITR0 |

| TIM2_TRGO                          | TIM0_ITR2                        | TIM1_ITR2 |           | TIM3_ITR2 | TIM4_ITR1 | 1         | 1         | TIM9_ITR1 |

| TIM3_TRGO                          | TIM0_ITR3                        | TIM1_ITR3 | TIM2_ITR3 | -         | TIM4_ITR2 | TIM7_ITR2 | TIM8_ITR0 | TIM9_ITR2 |

| TIM4_TRGO                          | TIM0_ITR0                        | -         | TIM2_ITR2 | -         | •         | TIM7_ITR3 | TIM8_ITR1 | -         |

| TIM7_TRGO                          | -                                | TIM1_ITR1 | -         | TIM3_ITR3 | TIM4_ITR3 | -         | -         | -         |

| TIM8_TRGO                          | -                                | -         | -         | -         | -         | -         | •         | TIM9_ITR3 |

| TIM9_TRGO                          | -                                | -         | -         | -         | -         | -         | TIM8_ITR3 | -         |

表 5-2: 定时器内部互联触发信号

AN2402 TIM 使用注意要点

## 5.3 从定时器时钟源边沿

对于从定时器的时钟源信号,除了外部触发输入(ETRF)可以设置为上升/下降沿有效,其余信号都是上升沿有效。

AN2402 版本维护

# 6 版本维护

| 日期         | 版本   | 描述  |

|------------|------|-----|

| 2023.09.14 | V1.0 | 初始版 |

|            |      |     |

|            |      |     |

|            |      |     |

|            |      |     |