# UM2080F32 硬件调试指南

版本: V1.1

广芯微电子(广州)股份有限公司

http://www.unicmicro.com/

AN1501 条款协议

### 条款协议

本文档的所有部分,其著作产权归广芯微电子(广州)股份有限公司(以下简称广芯微电子) 所有,未经广芯微电子授权许可,任何个人及组织不得复制、转载、仿制本文档的全部或部分组件。 本文档没有任何形式的担保、立场表达或其他暗示,若有任何因本文档或其中提及的产品所有资讯 所引起的直接或间接损失,广芯微电子及所属员工恕不为其担保任何责任。除此以外,本文档所提 到的产品规格及资讯仅供参考,内容亦会随时更新,恕不另行通知。

- 本文档中所记载的关于电路、软件和其他相关信息仅用于说明半导体产品的操作和应用实例。

用户如在设备设计中应用本文档中的电路、软件和相关信息,请自行负责。对于用户或第三方因使用上述电路、软件或信息而遭受的任何损失,广芯微电子不承担任何责任。

- 2. 在准备本文档所记载的信息的过程中,广芯微电子已尽量做到合理注意,但是,广芯微电子并不保证这些信息都是准确无误的。用户因本文档中所记载的信息的错误或遗漏而遭受的任何损失,广芯微电子不承担任何责任。

- 3. 对于因使用本文档中的广芯微电子产品或技术信息而造成的侵权行为或因此而侵犯第三方的专利、版权或其他知识产权的行为,广芯微电子不承担任何责任。本文档所记载的内容不应视为对广芯微电子或其他人所有的专利、版权或其他知识产权作出任何明示、默示或其它方式的许可及授权。

- 4. 使用本文档中记载的广芯微电子产品时,应在广芯微电子指定的范围内,特别是在最大额定值、电源工作电压范围、热辐射特性、安装条件以及其他产品特性的范围内使用。对于在上述指定范围之外使用广芯微电子产品而产生的故障或损失,广芯微电子不承担任何责任。

- 5. 虽然广芯微电子一直致力于提高广芯微电子产品的质量和可靠性,但是,半导体产品有其自身的具体特性,如一定的故障发生率以及在某些使用条件下会发生故障等。此外,广芯微电子产品均未进行防辐射设计。所以请采取安全保护措施,以避免当广芯微电子产品在发生故障而造成火灾时导致人身事故、伤害或损害的事故。例如进行软硬件安全设计(包括但不限于冗余设计、防火控制以及故障预防等)、适当的老化处理或其他适当的措施等。

AN1501 目录

## 目录

| 1 | 概还          |                 | 1  |

|---|-------------|-----------------|----|

| 2 | 应用参         | ⇒考原理图           | 2  |

|   | 2.1         | BUCK 模式         | 2  |

|   | 2.2         | 非 BUCK 模式       | 3  |

|   | 2.3         | 参考电路概述          | 4  |

|   | 2.4         | 物料清单            | 4  |

| 3 | 硬件设         | t计              | 7  |

|   | 3.1         | PCB Layout      | 7  |

|   | 3.2         | Layout 建议       | 8  |

| 4 | 接收四         | - 配调试           | g  |

|   | 4.1         | RX 模式下 LNA 输入阻抗 | g  |

|   | 4.2         | 匹配网络结构          | g  |

|   | 4.3         | 实际测试调整          | 11 |

| 5 | 发射四         | 配调试             |    |

| 6 | <b>临</b> 木华 |                 | 16 |

AN1501 概述

## 1 概述

UM2080F32 是广芯微电子(广州)股份有限公司研制的基于 ARM Cortex-M0+内核的超低功耗、高性能的、单片集成(G)FSK/OOK 无线收发机的 32 位 SoC 芯片。UM2080F32 工作于200MHz~960MHz 范围内,支持灵活可设的数据包格式,支持自动应答和自动重发功能,支持跳频操作,支持 FEC 功能,同时内部集成了完整的射频接收机、射频发射机、频率综合器、调制解调器,用户只需配备简单、低成本的外围器件就可以获得良好的收发性能。此外,UM2080F32 内部还集成了CAN、12 位 SAR ADC、UART、SPI、QSPI、I2C 等通用外围通讯接口,ADC、OPA、比较器等传感获取接口,以及 LPTIMER、WDT 等超低功耗模块接口,并内置 RC 高频和低频振荡器。芯片系统采用了独特的低功耗设计技术,具有高整合度、高抗干扰、高可靠性和超低功耗等技术特点。支持 Keil MDK 集成开发环境,支持 C 语言和汇编语言进行软件开发。

# 2 应用参考原理图

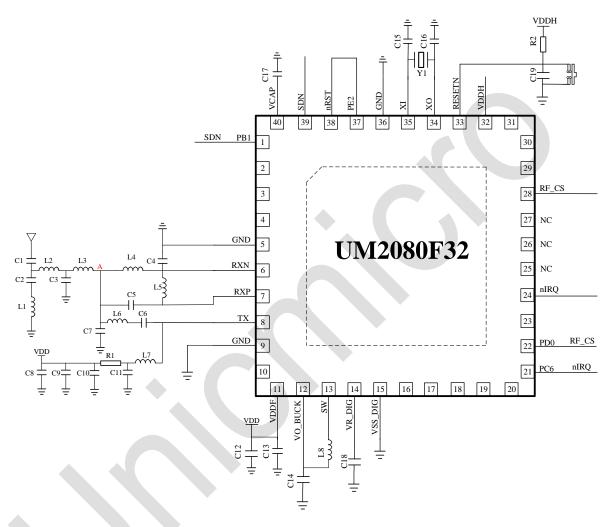

## 2.1 BUCK 模式

图 2-1: BUCK 模式应用参考原理图

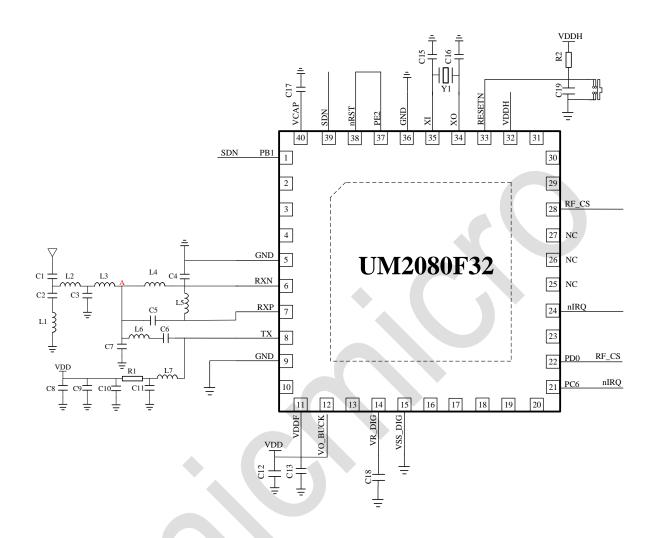

#### 2.2 非 BUCK 模式

图 2-2: 非 BUCK 模式应用参考原理图

UM2080F32 提供两种电源工作模式:

#### (1) 非 BUCK 模式

外部的L8功率电感不需要,芯片SW脚悬空,VO\_BUCK脚和外部电源直连。在这种模式下,芯片内部的LDO由外部电源直接供电,BUCK DC-DC需配置在关闭模式(Reg1B[1:0]=00)。

#### (2) BUCK 模式

芯片 SW 脚和 VO\_BUCK 脚之间接 L8 功率电感, VO\_BUCK 脚和外部电源断开, VO\_BUCK 脚外接 C14(10uF)对地电容,R1 贴  $4.7\Omega$  电阻。在这种模式下,芯片内部的 LDO 由 VO\_BUCK 供电。

### 2.3 参考电路概述

- L7 是扼流电感。

- C8-C13 是电源退耦电容,用于减少 PA 输出对电源的影响。根据实际的应用需求要做适当调整。

- C1 是隔直电容,并且与 L6 的部分电感在工作频点形成谐振起到谐波抑制作用。

- 图 2-1 和图 2-2 中标识的 A 点为直连点,该点的阻抗是 50Ω。

- L6、L7、C6 组成 TX 匹配网络,实现 PA 输出和直连点阻抗匹配。

- L4, L5, C4, C5 组成 RX 巴伦匹配网络,实现接收机的输入阻抗和直连点匹配,并使得接收信号到达差分输入口 RXP 和 RXN 处时幅度相等,相位相差 180 度。

- L1、L2、L3、C1、C2、C3 为 50Ω 到 50Ω 的切比雪夫低通滤波匹配网络。

- Y1 推荐用频率容差±10ppm 的 30MHz 或者 26MHz 晶体,可接受的晶体频率容差取决于用户 产品通讯系统的要求,如频率,信道,带宽等。

- C15、C16 为晶振负载电容,根据实际晶振型号来取值。

- C14、L8 为 BUCK DCDC 滤波电路。

### 2.4 物料清单

表 2-1: +18dBm 物料清单

| <i>1</i> 2- D | 描述                           | 元件值  |        |       |       | 单位  |

|---------------|------------------------------|------|--------|-------|-------|-----|

| 位号            |                              | 315  | 433.92 | 868   | 915   | MHz |

| C1            | ±10%,0402, X7R,50V,YAGEO     | 27nH | 20pF   | 5.6nH | 5.6nH | -   |

| C2            | ±5%, 0402, C0G, 50 V,YAGEO   | 5    | 2.7    | 3.3   | 3.3   | pF  |

| C3            | ±5%, 0402, C0G, 50 V,YAGEO   | 8.2  | 8.2    | 6     | 6     | pF  |

| C4            | ±5%, 0402, C0G, 50 V,YAGEO   | 4.7  | 8.2    | 3.3   | 3.3   | pF  |

| C5            | ±5% ,0402,NP0, 50V,YAGEO     | 5.6  | 3      | 3     | 3     | pF  |

| C6            | ±1%,0402,NPO,50V,muRata      | 8.2  | 5.6    | 4.7   | 4.7   | pF  |

| C7            | ±5%,0402,NPO,50V,YAGEO       | 3.3  | 3      | 6.8   | 6.8   | pF  |

| C8            | ±10%,0402,X7R,50V,FH(风华)     | 470  | 470    | 470   | 470   | pF  |

| C9            | ±5%, 0603 NP0, 50 V,SAMSUNG  | 100  | 100    | 100   | 100   | nF  |

| C10           | ±10%,0402,X7R,50V,SAMSUNG    | 2.2  | 2.2    | 2.2   | 2.2   | μF  |

| C11           | ±10%,0402,X7R,50V,SAMSUNG    | 2.2  | 2.2    | 2.2   | 2.2   | μF  |

| C12           | ±10%,0402,X7R,50V,SAMSUNG    | 100  | 100    | 100   | 100   | nF  |

| C13           | ±5%, 0402, C0G, 50 V,SAMSUNG | 470  | 470    | 470   | 470   | pF  |

| C14           | ±5%, 0402, C0G, 50 V,SAMSUNG | 10   | 10     | 10    | 10    | uF  |

| 位号     | 描述                        | 元件值 |        |     |     | 单位    |

|--------|---------------------------|-----|--------|-----|-----|-------|

| 174. 之 |                           | 315 | 433.92 | 868 | 915 | MHz   |

| C15    | ±10%,0402,X7R,50V,YAGEO   | 20  | 20     | 20  | 20  | pF    |

| C16    | ±10%,0402,X7R,50V,YAGEO   | 20  | 20     | 20  | 20  | pF    |

| C17    | ±10%,0402,X7R,50V,SAMSUNG | 4.7 | 4.7    | 4.7 | 4.7 | μF    |

| C18    | ±10%,0402,X7R,50V,SAMSUNG | 10  | 10     | 10  | 10  | nF    |

| C19    | ±10%,0402,X7R,50V,SAMSUNG | 1   | 1      | 1   | 1   | μF    |

| L1     | ±2%,0402,贴片绕线电感,Sunlord   | 12  | 10     | 0R  | 0R  | nH    |

| L2     | ±2%,0402,贴片绕线电感,Sunlord   | 47  | 33     | 10  | 10  | nH    |

| L3     | ±2%,0402,贴片绕线电感,Sunlord   | 22  | 22     | 8.2 | 8.2 | nH    |

| L4     | ±5%,0402,贴片绕线电感,Sunlord   | 68  | 33     | 10  | 10  | nH    |

| L5     | ±5%,0402,贴片绕线电感,Sunlord   | 82  | 33     | 12  | 12  | nH    |

| L6     | ±5%,0603,贴片绕线电感,Sunlord   | 33  | 22     | 8.2 | 8.2 | nΗ    |

| L7     | ±5%,0603,贴片绕线电感,Sunlord   | 220 | 180    | 100 | 100 | nΗ    |

| L8     | ±5%,0805,贴片绕线电感,Sunlord   | 4.7 | 4.7    | 4.7 | 4.7 | μH    |

| R1     | ±5%,0402,贴片电阻,YAGEO       | 4.7 | 4.7    | 4.7 | 4.7 | Ω     |

| R2     | ±5%,贴片电阻,0603, 100mW,     | 4.7 | 4.7    | 4.7 | 4.7 | ν0    |

| K2     | YAGEO                     | 4.7 |        |     |     | ΚΩ    |

| Y1     | 5032 贴片无源晶振±10PPM         | 30  | 30     | 30  | 30  | MHz   |

| YI     | 20pF,YXC(扬兴晶振)            |     |        |     |     | IVI□∠ |

表 2-2: 13dBm 物料清单

| 位号  | 描述                           | 元件值 |        |       |       | 单位  |

|-----|------------------------------|-----|--------|-------|-------|-----|

| 平子  |                              | 315 | 433.92 | 868   | 915   | MHz |

| C1  | ±10%,0402, X7R,50V,YAGEO     | 0R  | 20pF   | 5.6nH | 5.6nH | -   |

| C2  | ±5%, 0402, C0G, 50 V,YAGEO   | 5   | 2.7    | 2.7   | 2.7   | pF  |

| C3  | ±5%, 0402, C0G, 50 V,YAGEO   | 8.2 | 8.2    | 5     | 5     | pF  |

| C4  | ±5%, 0402, C0G, 50 V,YAGEO   | 4.7 | 8.2    | 2     | 2     | pF  |

| C5  | ±5% ,0402,NP0, 50V,YAGEO     | 5.6 | 3      | 2     | 2     | pF  |

| C6  | ±1%,0402,NPO,50V,muRata      | 8.2 | 5.6    | 4.7   | 4.7   | pF  |

| C7  | ±5%,0402,NPO,50V,YAGEO       | 3.3 | 3      | 3     | 3     | pF  |

| C8  | ±10%,0402,X7R,50V,FH(风华)     | 470 | 470    | 470   | 470   | pF  |

| C9  | ±5%, 0603 NP0, 50 V,SAMSUNG  | 100 | 100    | 100   | 100   | nF  |

| C10 | ±10%,0402,X7R,50V,SAMSUNG    | 2.2 | 2.2    | 2.2   | 2.2   | μF  |

| C11 | ±10%,0402,X7R,50V,SAMSUNG    | 2.2 | 2.2    | 2.2   | 2.2   | μF  |

| C12 | ±10%,0402,X7R,50V,SAMSUNG    | 100 | 100    | 100   | 100   | nF  |

| C13 | ±5%, 0402, C0G, 50 V,SAMSUNG | 470 | 470    | 470   | 470   | pF  |

| C14 | ±5%, 0402, C0G, 50 V,SAMSUNG | 10  | 10     | 10    | 10    | uF  |

| C15 | ±10%,0402,X7R,50V,YAGEO      | 20  | 20     | 20    | 20    | pF  |

| C16 | ±10%,0402,X7R,50V,YAGEO      | 20  | 20     | 20    | 20    | pF  |

| C17 | ±10%,0402,X7R,50V,SAMSUNG    | 4.7 | 4.7    | 4.7   | 4.7   | μF  |

| C18 | ±10%,0402,X7R,50V,SAMSUNG    | 10  | 10     | 10    | 10    | nF  |

| C19 | ±10%,0402,X7R,50V,SAMSUNG    | 1   | 1      | 1     | 1     | μF  |

| 位号 | 描述                      | 元件值 |         |     |       | 单位    |     |

|----|-------------------------|-----|---------|-----|-------|-------|-----|

| 不之 |                         | 315 | 433.92  | 868 | 915   | MHz   |     |

| L1 | ±2%,0402,贴片绕线电感,Sunlord | 12  | 10      | 2.7 | 2.7   | nH    |     |

| L2 | ±2%,0402,贴片绕线电感,Sunlord | 47  | 33      | 10  | 10    | nH    |     |

| L3 | ±2%,0402,贴片绕线电感,Sunlord | 68  | 39      | 8.2 | 8.2   | nH    |     |

| L4 | ±5%,0402,贴片绕线电感,Sunlord | 68  | 33      | 12  | 12    | nH    |     |

| L5 | ±5%,0402,贴片绕线电感,Sunlord | 82  | 33      | 12  | 12    | nH    |     |

| L6 | ±5%,0603,贴片绕线电感,Sunlord | 56  | 33      | 12  | 12    | nH    |     |

| L7 | ±5%,0603,贴片绕线电感,Sunlord | 220 | 180     | 100 | 100   | nH    |     |

| L8 | ±5%,0805,贴片绕线电感,Sunlord | 4.7 | 4.7     | 4.7 | 4.7   | μH    |     |

| R1 | ±5%,0402,贴片电阻,YAGEO     | 4.7 | 4.7     | 4.7 | 4.7   | Ω     |     |

| R2 | ±5%,贴片电阻,0603, 100mW,   | 4.7 | 4.7 4.7 | 4.7 | 4.7   | ΚΩ    |     |

|    | YAGEO                   |     | 4.7     |     |       |       |     |

| Y1 | 5032 贴片无源晶振±10PPM       | 30  | 20 20   | 30  | 30 30 | 30    | MHz |

|    | 20pF,YXC(扬兴晶振)          |     | 30      | 30  | 30    | IVI□∠ |     |

#### 注:

- 非 BUCK 模式: R1=0R, L8=NC。

- BUCK 模式: R1=4.7Ω, L8 推荐用 0805 以上封装的功率电感, 具体参数如上表。

AN1501 硬件设计

## 3 硬件设计

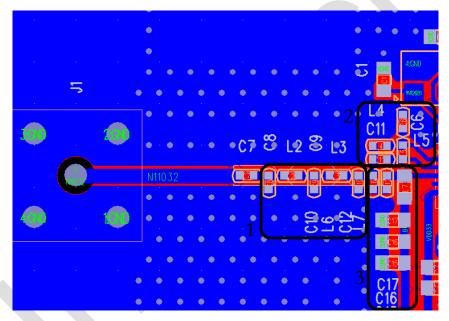

### 3.1 PCB Layout

UM2080F32 采用收发一体设计,发射和接收能够共用同一根天线,在不会显著影响收发性能的情况下,相较使用单独的收发通道,结构更紧凑,成本更低。通过芯片外接的匹配及滤波元器件的调整来获得较佳的发射和接收性能。图 3-1 中 PCB 采用 2 层板设计,黑色框 1 为滤波电路,可以有效的抑制各次谐波,满足认证要求;为有效提高接收性能,芯片内部接收电路采用差分设计,黑色框 2 为接收匹配巴伦部分。黑色框 3 为发射匹配元件(L6、C12、L7)及 RF 部分电源滤波元件。

图 3-1: PCB Layout 应用参考

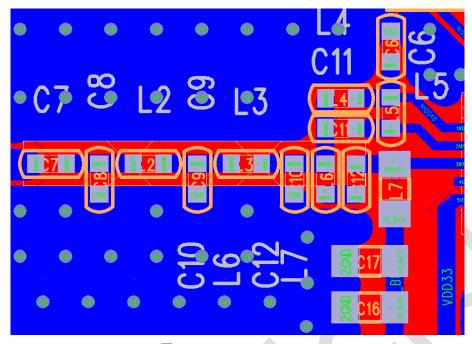

由于 RF 部分匹配的优劣直接决定所设计 PCB 线路板 RF 性能的好坏;在进行 PCB 布线时, 匹配元件尽量靠近芯片管脚且排列紧凑,以减少 PCB 走线寄生参数的影响,如图 3-2 所示。与 SMA 接头间连接走线要做好阻抗控制,走 50 欧姆 CPW。RF 部分滤波电容要尽量靠近芯片 TX 管 脚。在 RF 走线两边尽量保证有完整的接地平面并通过过孔与芯片底部接地焊盘通过底层完整地平 面连接在一起。 AN1501 硬件设计

图 3-2: RF 部分走线示意图

## 3.2 Layout 建议

- 1. 使用外部晶振时,晶振要靠近芯片 XTAL\_IN, XTAL\_OUT 管脚放置,晶振与芯片管脚的连线不宜过长。晶振周围要保持良好的接地面,周围不要走高频信号线。晶振下方需保留完整的接地面,尽量不要让走线从晶振下方穿过。

- 2. 使用 QFN40 封装芯片时,底部焊盘通过过孔与 GND Plane 连接。过孔孔径可适当的大一些,以增加焊接时的可靠性。

- 3. 所有接地管脚,尽量在同一完整地面或通过过孔与一完整地面相连。

电源滤波电容尽量靠近芯片管脚,电源线走线路径要经由电容后再到芯片管脚,需符合 PCB Layout 走线规范。可在电源线靠近滤波电容处增加磁珠或其它滤波电路来提高电源的稳定性。

AN1501 接收匹配调试

## 4 接收匹配调试

### 4.1 RX 模式下 LNA 输入阻抗

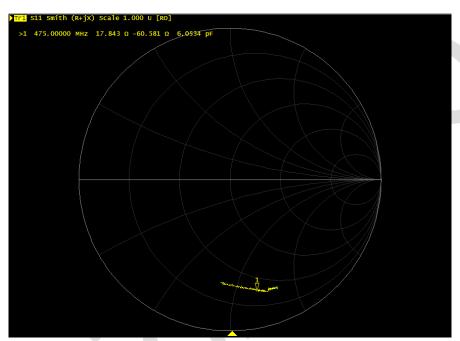

在接收模式下,使用网络分析仪直接测量 UM2080F32 差分输入引脚 RX<sub>P</sub>/RX<sub>n</sub> 的输入阻抗,结果如下图所示。

图 4-1: 测量输入阻抗

测量时需要将网络分析仪的输出功率设置在-25dBm 以下,以保证 LNA 的输入功率在其线性工作范围内。输入功率太大时会导致所测试的阻抗数据失真。

由测量得到的阻抗数据可以将 LNA 的输入阻抗等效为一个电阻 RLNA 与一个电容 CLNA 并联。

从图中的差分输入阻抗Z=R+jX,将其转换为导纳 $Y=\frac{1}{Z}=G+jB$ 。由此可以计算出等效的并联输入电阻和电容值 $R_{LNA}=\frac{1}{G},\;\;C_{LNA}=\frac{B}{2\pi f}$ 。

由图中测量的 S11 数据可以计算出在 475MHz 时,等效电阻 $R_{LNA}=223.55\Omega$ ,电容 $C_{LNA}=5.09pF$ 。

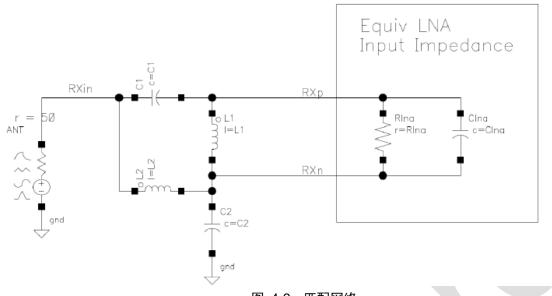

## 4.2 匹配网络结构

为了能达到较佳的接收性能,设计中采用 4 元匹配网络,如下图所示。该 4 元匹配网络可以在  $RX_P$  和  $RX_n$  之间产生理想的  $180^\circ$ 相位差,可以有效改善 LNA 转换增益和接收灵敏度。

AN1501 接收匹配调试

图 4-2: 匹配网络

我们要将输入阻抗匹配到 $Z_{IN}=50\Omega$ ,则输入阻抗只有实部;此时输入电流 $I_{IN}$ 也是仅有实部。该输入电流通过 C2 在 RXn 节点处产生电压 $V_{RXn}$ ,此时电压 $V_{RXn}$ 相对于输入有-90°相移。由于是差分输入要求 RXP 和 RXN 之间电压幅度相等相位相反。如果 $V_{RXn}$ 相位是-90°,则 $V_{RXp}$ 相位就必须是+90°。由于 LNA 输入阻抗并不是纯电抗,通过 LNA 网络的电流与通过 C2 产生的电流会有不同,使得相位并不是严格的-90°。一般的巴伦使用 3 个元件 L1、C1、C2,此时 LAN 两端的相位并不能达到我们所需要的反相位。引入 L2 对相位进行补偿,使 LNA 差分输入端电压保持相反的相位。

可通过如下公式对元件值进行计算:

$$L_2 = \frac{\sqrt{50\Omega \times R_{LNA}}}{\omega_{RF}}$$

$$C_1 = \frac{1}{\omega_{RF}^2 L_2}$$

$$C_2 = 2 \times C_1$$

$$L_{LNA} = \frac{1}{\omega_{RF}^2 C_{LNA}}$$

$$L_M = 2 \times L_2$$

$$L_1 = \frac{L_{LNA} L_M}{L_{LNA} + L_M}$$

使用上述公式,可计算得到在 433MHz, 4 元匹配网络元件的参数如下:

$$C_1 = 3.17pF$$

$L_1 = 16.84nH$

$C_2 = 6.34pF$

$L_2 = 35.44nH$

AN1501 接收匹配调试

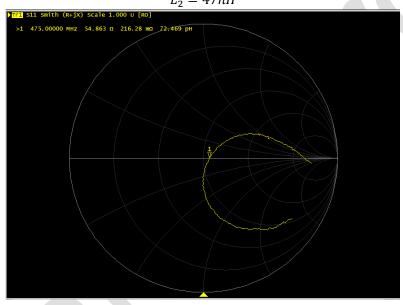

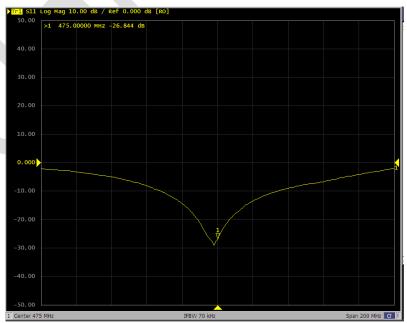

## 4.3 实际测试调整

以上述通过理论计算的值作为参考,实际上选择在该值附近的实际的电感电容。由于实际 PCB 上布局走线引入的寄生影响,实际的元件值还需要在此基础上进行调整。

在接收模式下,在测试板上通过调整参数,使用网络分析测量的 S11 结果如下图所示。 实际的匹配元件取值为:

$C_1 = 3pF$   $L_1 = 18nH$   $C_2 = 20pF$   $L_2 = 47nH$

图 4-3: 匹配结果

## 5 发射匹配调试

为了能够在供电电压 $V_{DD}=3.3V$ 时获得最大的输出功率和最大的输出效率(最小电流消耗),并满足相关法规对辐射杂散的要求,需要对电路输出进行相应的匹配设计。

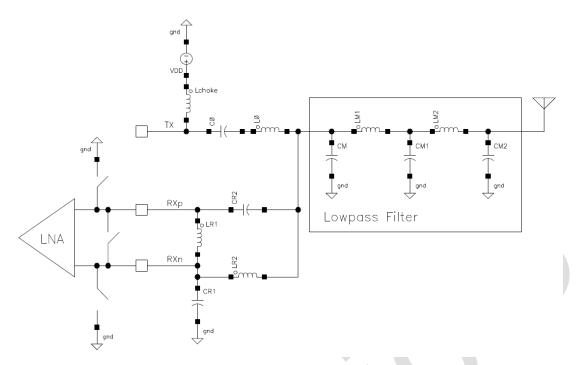

#### UM2080F32 有发射和接收的功能,发射和接收可以有 3 种不同的连接方式。

- 1. TX 和 RX 分别为独立的 2 路, 使用 2 根天线, 分别来进行发射和接收。

- 2. TX 和 RX 通过一个 RF 开关连接在一起, 使用 1 根天线, 通过控制开关的方向来控制信号到 TX 或 RX 的走向。

- 3. TX 和 RX 通过走线直接连接在一起, 使用 1 根天线。

在 UM2080F32 内部的 PA 电路不是传统的 Class A/B/C 类线性功放,使用的是开关 Class E 类功放,可以获得很高的效率,其匹配方法也不同于传统的线性功放。

#### Class E 匹配主要步骤如下:

- 1. 选择 $L_{CHOKE}$ (上拉电感)在 $F_0$ 产生高阻抗负载。

- 2. 选择 $C_0$ - $L_0$ (串联谐振电感电容)谐振在频率 $F_0$ 。

- 3. 计算 $L_X$  (串联电感)、 $C_M$  (并联电容),做负载匹配。

- 4. 设计切比雪夫低通滤波器(衰减谐波)。

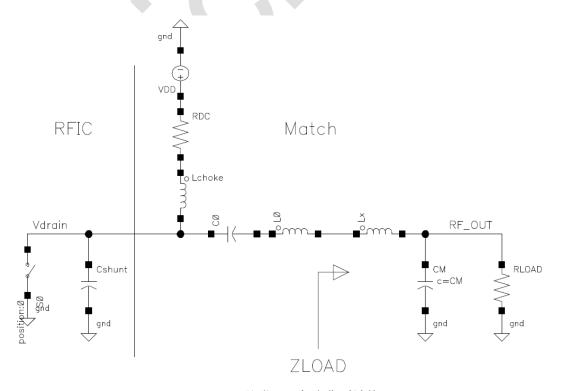

图 5-1: 开关类 PA 电路典型结构

对于 Class-E 开关功放,上拉电感 $L_{CHOKE}$ 的阻抗理论上在 DC 时为 0,在其他频率为无穷大。在实际上,我们可以选择某些电感值以近似达到该效果。在选择 $L_{CHOKE}$ 时,使其不仅在主频为高阻抗,在较低阶谐波也为高阻。电感值也不要太大导致其并联谐振频率在主频或超过主频。

串联电容电感 $C_0$ - $L_0$ 使其谐振在主频 $F_0$ 。理论上有很多种 LC 的组合可以谐振在该频率,在选择元件值时,取值不要特别大或特别小。同样的在理论上希望 $C_0$ - $L_0$ 在谐振频率阻抗为 0,在其他频率阻抗为无穷大。在实际应用中可使用高 L/C 值来达到合理近似。为了减少谐振电路的插损,希望其Q 值尽量高,实际元件电感 Q 值要小于电容 Q 值,取 $L_0$ - $C_0$ 比值时使电感 Q 值最大。一般电感 Q 值随着其取值的增加而增大,在增大电感时不要超过其自谐振频率。

理论上 Class-E 开关功放,其要求的负载阻抗 $(Z_{LOAD})$ 为漏极并联电容 $(C_{SHUNT})$ 和工作频率 $(\omega_0 = 2\pi F_0)$ 的函数。

$$Z_{LOAD} = (\frac{0.2815}{\omega_0 C_{SHUNT}}) e^{j \times 49.0524^{\circ}}$$

UM2080F32 的并联电容约为 2.5pF, 代入公式计算可得:

$$Z_{LOAD} = \left(\frac{0.2815}{2\pi \times 475M \times 2.5nF}\right) e^{j \times 49.0524^{\circ}} = 24.73 + j28.5\Omega$$

然后计算匹配元件 $L_X$ 和 $C_M$ 的值将天线端阻抗 $Z_{ANT}$ 匹配到所需负载阻抗 $Z_{LOAD}$ 。理想天线负载阻抗为 $Z_{ANT}=R_{ANT}=50\Omega$ ,可使用 Smith Chart 得 $C_M=6.77pF$ , $L_X=17.81nH$ 。

串联电感 $L_0$ 和 $L_x$ 可以合并使用一个等效电感 $L_0 + L_x$ 来代替。

匹配网络可以使用贴片绕线电感或贴片叠层电感。绕线电感相较叠层电感有更高的 Q 值及更小的直流电阻,使用绕线电感可以获得更好的性能,但其物料价格也相较叠层电感贵。在实际使用时需综合考虑性能和成本来选择使用哪种电感。

低通滤波选用切比雪夫滤波器,在高频阻带衰减和带内插损取得平衡,设计时通带内波纹设为 0.25dB~0.5dB。

基于成本考虑,我们在设计发射接收连接方式时优先选择第 3 种,即将 TX 和 RX 通过走线直接连接在一起。此情况下的匹配电路典型结构如图 5-2 所示,将接收端的差分匹配巴伦与 TX、RX 路径连接在一起。在该种情况下,我们希望在 TX 模式下,接收匹配电路不会对输出电路产生太大影响;同样的在 RX 模式下,发射匹配电路对接收性能也不要产生太大影响。如图 5-2 所示在芯片内部 LNA 输入端设有开关对 TX、RX 模式进行隔离。

图 5-2: TX、RX 直连匹配典型结构

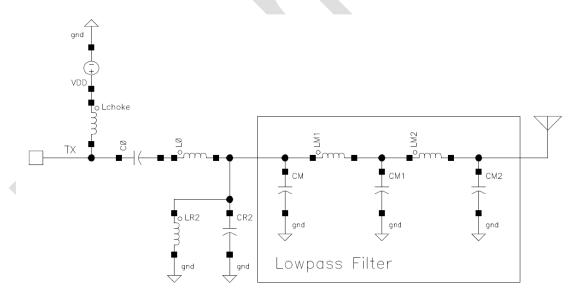

在 TX 模式时,3 个开关同步闭合,在其他模式时开关断开。其等效电路如图 5-3 所示。此时  $L_{R2}$ 和 $C_{R2}$ 等效并联到地。当选取的 $L_{R2}$ 和 $C_{R2}$ 值谐振在工作频率时,其在 TX 路径上呈现高阻,因此会 将接收匹配网络对发射的影响减小。

图 5-3: TX 模式等效电路图

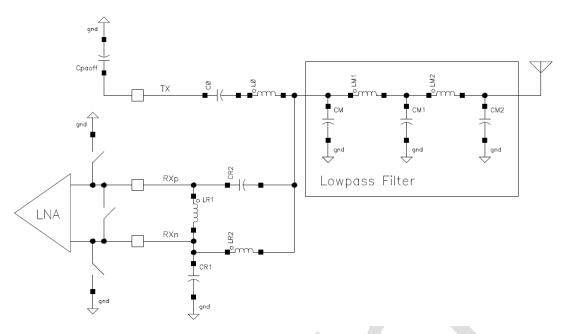

在 RX 模式时,PA 输出关闭,其等效电路图如图 5-4 所示。此时 $C_{PAoff}$ 与 $C_0$ 、 $L_0$ 串联在一起,在其谐振频率相当于对地短路,从而影响接收性能。在 $C_{PAoff}$ 固定的情况下,需要通过调整 $C_0$ 、 $L_0$ 的取值,在稍微牺牲发射性能的同时降低对接收性能的影响。可调整增大 $L_0$ 的取值来对性能进行优化。

图 5-4: RX 模式等效电路图

AN1501 版本维护

# 6 版本维护

| 版本   | 日期         | 描述          |

|------|------------|-------------|

| V1.0 | 2022.07.20 | 初始版         |

| V1.1 | 2023.10.16 | 更新应用参考原理图章节 |

|      |            |             |

|      |            |             |

|      |            |             |